简单介绍了计算机是什么,计算机的发展过程,组成,结构关系,工作过程,硬件技术指标。内容有点多,概述已经写在了本文开头的目标中。

目标

2.理解计算机系统的多层次结构和虚拟机的概念

3.理解计算机组成与计算机体系结构的关系

5.初步理解存储器,运算器和控制器的组成与功能,并能描述运算器加、减、乘、除四则运算的操作过程

6.能正确绘制细化的计算机硬件组成框图,并能基于此图描述主机完成一条指令(如存数、取数、加法、减法)的过程

关于计算机

什么是电子计算机?

能存储程序和数据,能执行机器指令,能自动、高速、精确进行信息处理的现代化电子设备。

计算机有多种分类方法

按用途(专用,通用)

按规模(个人,小型,大型,巨型)

按处理的信号(数据信号,模拟信号)

按体系结构

SISD(Single instruction, Single data)单指令单数据流

SIMD(Single Instruction,Multiple Data)单指令多数据流

MISD(Multiple Instruction,Single Data)多指令单数据流

MIMD(Multiple Instruction,Multiple Data)多指令多数据流

计算机系统简介

1.计算机系统软硬件组成

1 | graph LR; |

2.从解题过程分析计算机层次结构

1 | graph LR; |

1 | graph LR; |

1 | graph LR; |

3.计算机的层次结构

1 | graph TB; |

计算机的基本组成

1.冯·诺依曼计算机的特点

1.计算机由运算器,控制器,存储器,输入设备,输出设备五大部件组成。(硬件组成)

2.指令和数据以同等地位存于存储器,可按地址寻访。(存储特点)

3.指令和数据用二进制表示。(编码特点)

4.指令由操作码和地址码组成,操作码用来表示操作的性质,地址码用来表示操作数在存储器中的位置。(指令格式)

5.指令在存储器中按顺序存放。(便于顺序执行)

6.机器以运算器为中心,I/O设备与存储器之间的数据传送通过运算器完成。(结构特点)

2.计算机的硬件框图

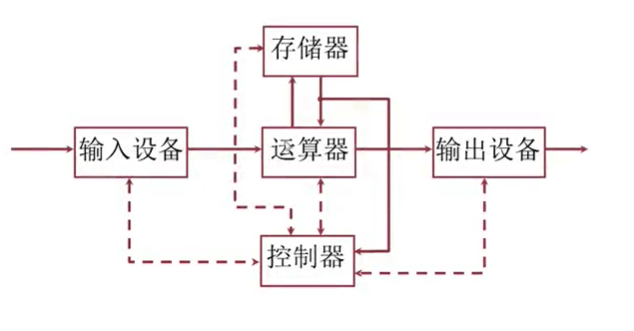

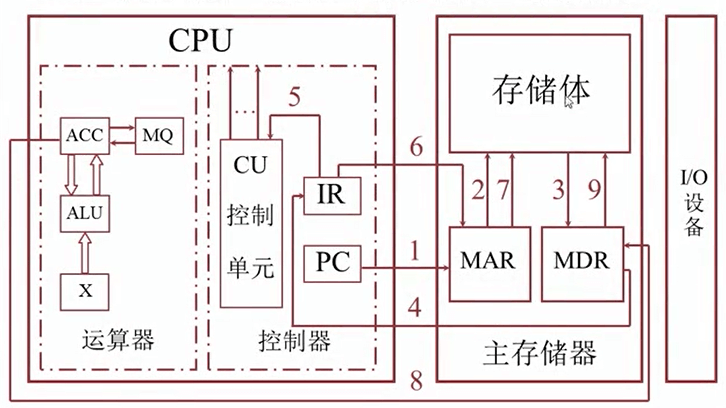

1.典型的冯·诺依曼计算机结构框图

实线表示数据信息,虚线表示控制信息

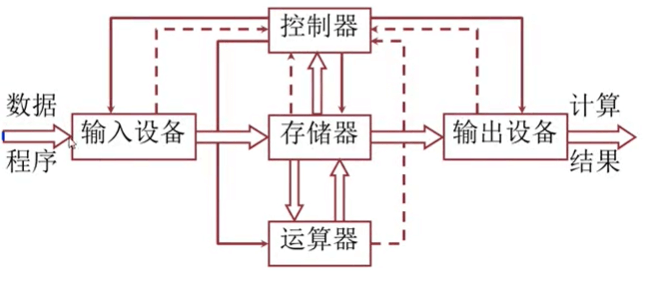

2.以存储器为中心的计算机结构框图

空心箭头表示数据信息,实线表示控制信息,虚线表示控制器之外的其他设备向控制器所做的反馈信息,如设备状态等

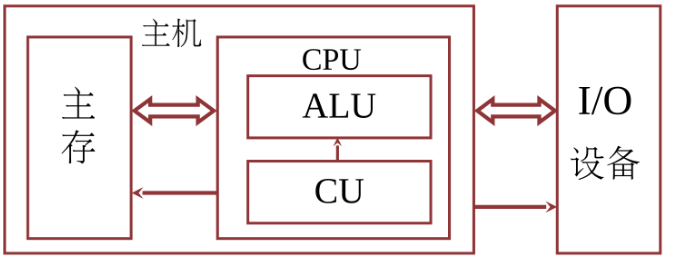

3.现代计算机的组成框图

1 | graph LR; |

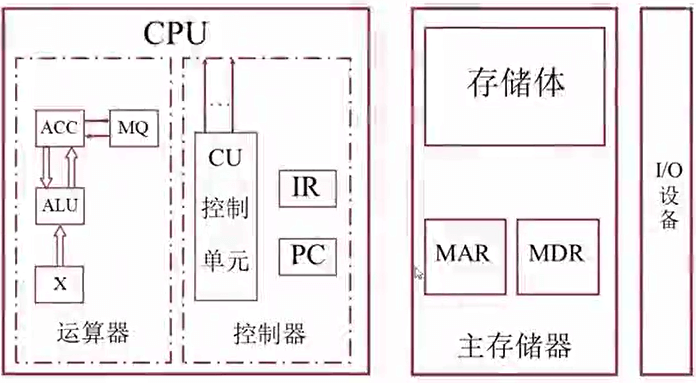

3.计算机各部件的组成

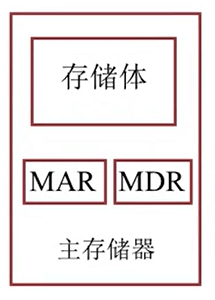

3.1存储器的基本组成

1.存储体(大楼) - 存储单元(房间) - 存储元件(床位)

存储单元 存放一串二进制代码,按地址寻访

2.MAR 存储器地址寄存器,其位数反映存储单元的个数

3.MDR存储器数据寄存器,其位数反映存储字长

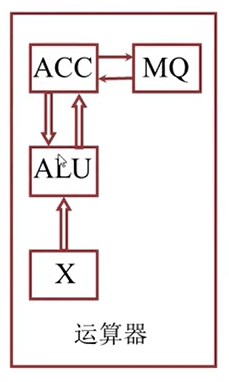

3.2运算器的基本组成及操作过程

ALU:算数逻辑单元

ACC:累加器

MQ:乘商寄存器

X:操作数寄存器

1.加法操作过程

1 | graph LR; |

第1步:初态 ACC中已经置好了被加数

第2步:把内存M单元中的数据取过来装入到X中 [M]–>X

第3步:ACC提供被加数,X提供加数,由ALU完成运算后放入ACC中,这就是第1步中已经存在数据的由来 [ACC]+[X]–>ACC

tip:M表示加数的地址,加上方括号的[M]表示该地址存放的数据,也就是加数本身

2.减法操作过程(与加法极其相似)

1 | graph LR; |

第1步:初态 ACC中已经置好了被减数

第2步:**[M]–>X**

第3步: [ACC]-[X]–>ACC

3.乘法操作过程

由于乘法的操作比较复杂,比如16位乘16位可能得到一个32位的数,所以存放的时候需要用到两个16位的寄存器,把高位(前16位)放到ACC中,把低位(后16位)放到MQ中

1 | graph LR; |

第1步:初态 ACC中已经置好了被乘数

第2步:**[M]–>MQ**

第3步:**[ACC]–>X**

第4步:0–>ACC(清空ACC)

第5步:**[X][MQ]–>ACC//MQ*

4.除法操作过程

MQ中存放商,ACC中存放余数

1 | graph LR; |

第1步:初态 ACC中已经置好了被除数

第2步:**[M]–>X**

第3步:**[ACC]/[X]–>MQ** 余数在ACC中

运算器操作过程总结

| ACC | MQ | X | |

|---|---|---|---|

| 加法 | 被加数,和 | 加数 | |

| 减法 | 被减数,差 | 减数 | |

| 乘法 | 乘积高位 | 乘数,乘积低位 | 被乘数 |

| 除法 | 被除数。余数 | 商 | 除数 |

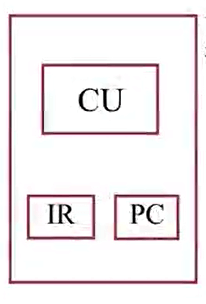

3.3控制器的基本组成

CU:控制单元

IR:指令寄存器,存放着当前欲执行的完整指令,操作码+地址码

PC:程序计数器,存放当前欲执行的指令地址,有计数功能,指向下一条指令地址,实现指令的顺序执行(PC)+1-->PC

第1步:PC给出指令的地址,CU根据地址在主存中取出该指令,放入到IR

第2步:CU从IR中取出指令的操作码,进行分析,根据分析结果发出控制信息

1 | graph LR; |

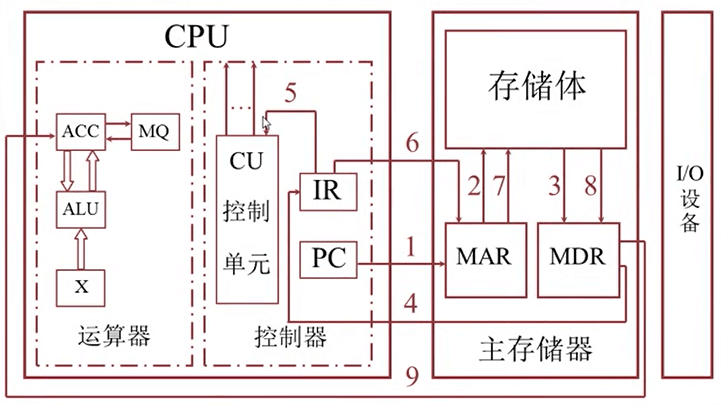

更细化的计算机硬件组成框图:

计算机的工作过程

大致逻辑:取指令-分析指令-执行指令

取数指令

主机完成一条指令的过程,以取数指令为例

通过计算机各部件的组成的1、2、3节,我们了解到存储器,运算器和控制器的工作过程,接下来是更完整的组成框图的工作过程。

取指令

第1步:PC–>MAR,PC给出指令的地址,放入到MAR中。

第2步:MAR–>存储体,根据MAR中的地址,通过译码,选中存储体中的地址存储单元。

第3步:存储体–>MDR,把锁定的地址的内容放入到MDR中。

第4步:MDR–>IR,(这里PC发出的地址可能是指令,也有可能是数据,我们以取数指令为例)将MDR中的指令放入到IR中。

分析指令

第5步:IR–>CU,当IR接收到指令之后,提交到CU,并由CU来分析接下来要执行什么操作。

执行指令

第6步:IR–>MAR,根据冯·诺依曼计算机的特点,指令包括操作码和地址码,CU根据操作码完成分析,发现这是一条取数的指令,再由地址码要求IR取出操作对象。

第7步:MAR–>存储体,MAR通过译码,在存储体中找到相应的存储单元。

第8步:存储体–>MDR,在存储单元中,取出数据,放入到MDR中。

第9步:MDR–>ACC,将数据传给ACC,等待运算处理。

存数指令

主机完成一条指令的过程,以存数指令为例

与取数指令比较,大致流程相同,直到第7步,MAR中的地址锁定存储体的存储单元位置之后,存数指令需要将数据放入到存储体中。

执行指令

第8步:ACC–>MDR,将ACC中的数据放入到MDR中。

第9步:MDR–>存储体,将MDR中的数据,放入到锁定的存储单元位置,完成存数。

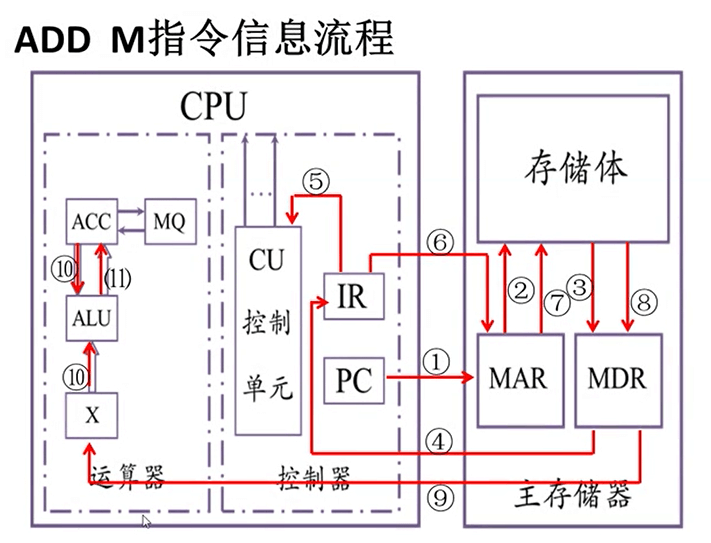

例题1 加法指令的信息流程

以加法指令ADD M(M为主存地址)为例,写出完成指令的信息流程(从取指令开始)

答案

点击查看

取指令:PC–>MAR–>M–>MDR–>IR

分析指令:OP(IR)–>CU

执行指令:Ad(IR)–>MAR–>M–>MDR–>X,ACC–>ALU同时X–>ALU,ALU–>ACC

例题2 指令和数据如何区分

指令和数据都在于存储器中,计算机如何区分它们?

答案

点击查看

方法1:根据不同阶段去区分,取指阶段取的是指令,执行阶段取的是数据;

方法2:根据地址的来源区分,来自PC寄存器的地址取的是指令,来自IR寄存器的地址码部分的地址取的是数据。

一个程序的运行过程

1 | graph TB; |

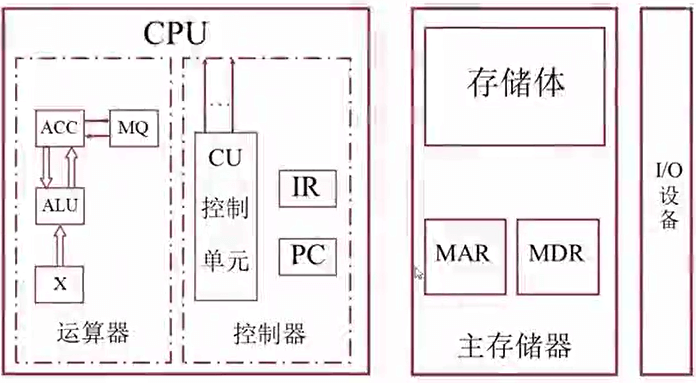

例题3 计算位数,指出信息通路

设主存储器容量为64K*32位,并且指令字长、存储字长、机器字长三者相等,写出图中各寄存器的位数,并指出那些寄存器之间有信息通路。

答案

点击查看

分析:

64K*32位:主存储器由64K个存储单位构成,每个存储单位可以存放一个字长为32位的存储字。(一栋楼,有64个房间,每个房间有32张床)

指令字长 = 存储字长 = 机器字长 =32位

64K个存储单元编号需要几位二进制数?

1K = 210

64 = 26

64K = 26 * 210 = 216

也就是64K需要16个二进制数来表示,也就是64个房间的编号,从0000……0(16个)到1111……1(16个)。

这个地址从哪儿来?

PC(上步推导得 16位)

访存时该地址存放在哪儿?

MAR(由PC输入,所以也是16位)

从我个人角度理解,存放数据的都是32位,存放地址的都是16位。至于信息通路已经由例题1和例题2演示了。

最终答案

计算机硬件的技术指标

机器字长

概念

CPU一次能处理的位数,与CPU中的寄存器位数有关。

对其他字长的概念理解

存储字长:存储器中一个存储单元(存储地址)所存储的二进制代码的位数,MDR寄存器的位数取决于存储字长。

指令字长:计算机指令字的位数,IR寄存器的位数取决于指令字长。

数据字长:计算机中一个特定的类型数据所存储所占用的位数。

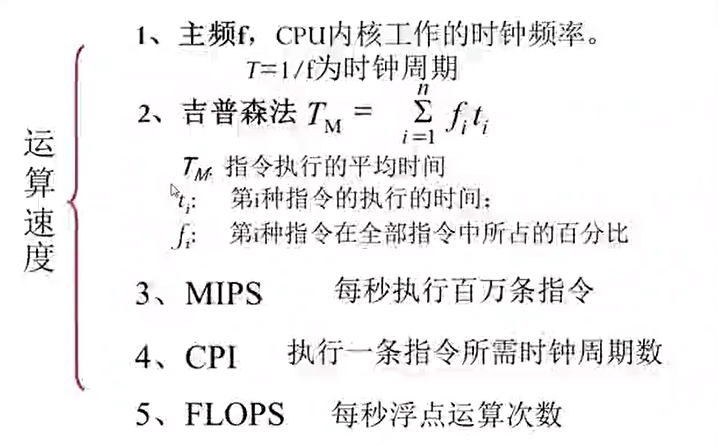

运算速度

指标

对运算速度的理解

1.主频、外频二者的关系

主频:CPU内核工作的时钟频率

外频:系统总线时钟频率

主频 = 外频*倍频系数

主频不能单独决定运算速度的快慢

2.主频,MIPS与CPI的关系

MIPS:百万条指令/每秒。

MIPS = f * 10-6/CPI

例题

莫计算机主频为1GHz,在其上运行的某目标代码含2*10^5条指令,共有A、B、C、D四类指令,每类指令的CPI值及其在目标代码中所占比例如下表,求目标代码的运行速度MIPS。

| 指令类型 | CPI | 所占比例 |

|---|---|---|

| A | 1 | 60% |

| B | 2 | 18% |

| C | 4 | 12% |

| D | 8 | 10% |

答案

点击查看

解:MIPS = f * 10-6/CPI

= 1*109*10-6/(1*60%+2*18%+4*12%+8*10%)

= 1000/2.24

= 446.4

存储容量

概念

存储器存放二进制信息的总位数

1 | graph TB; |